在半导体产业中,存在一种常被外界简化理解的“技术平移”假象——认为同属存储大类下的不同分支,其制造能力可以自然转换。近期,国内NAND厂商布局DRAM领域的动向备受关注,然而产业内部对此普遍持审慎态度。一个常见的误解是:既然同属存储芯片,NAND与DRAM的技术和产线理应互通。但实际情况是,二者在产品架构、工艺路径和制造逻辑上存在本质差异。

业界专家比喻,从DRAM延伸至NAND如同掌握高阶技术后向相对标准化领域拓展;而反向从NAND攻坚DRAM,则近似于在积累了规模化建造经验后,试图攻克精密仪器的极限制造——这不仅是技术路径的转换,更是对工艺精度、材料体系和制造稳定性要求的系统性跃升。

即便有企业已推出工程样品,从单颗芯片到规模化稳定量产之间,仍横亘着需要长期攻坚的“制造鸿沟”。那么,从工程制造视角审视,从NAND Flash跨越到DRAM,乃至复杂度更高的HBM,中间究竟存在哪些必须突破的实质性壁垒?是否真如外界设想,只要有厂房与设备,产能便可自然平移?

今天,我们暂搁市场叙事,聚焦制造本质,理性拆解这条跨越之路必须穿越的几重核心关卡。

存储芯片的技术分水岭:DRAM为何成NAND厂商跨界最难啃的骨头

存储芯片并非同质化产品,DRAM与NAND在计算机系统架构中承担着截然不同的职责,二者各司其职、无法相互替代,而这种功能分野,更从根源上决定了二者制造工艺的天壤之别,其中DRAM的工艺难度尤为突出,构成了跨界攻坚的核心壁垒。

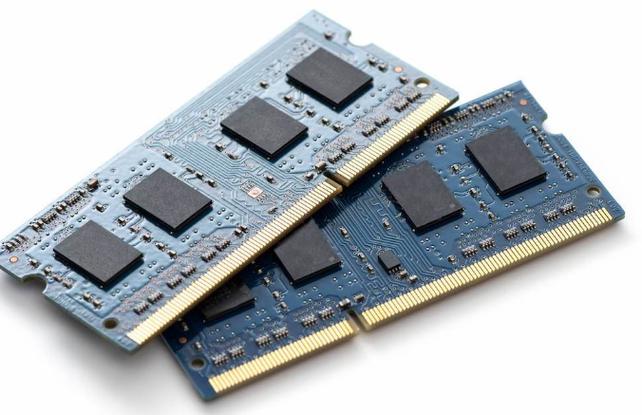

DRAM(随机存取存储器)堪称CPU与GPU的“高速中转站”,核心使命是实现极致的数据读写速度,以纳秒级响应完成数据吞吐与交换。无论是运行复杂的人工智能模型,还是处理高清视频渲染、大型游戏加载等重负载任务,DRAM的带宽表现与延迟控制都直接决定了计算效率的天花板。但为了追求极致速度,它不得不牺牲数据持久性——作为易失性存储,一旦切断电源,“中转站”内的所有数据会瞬间清零。

与之相对,NAND(闪存)则是整个系统的“海量仓库”,核心诉求是最大化存储容量与数据稳定性。即便完全断开电源,NAND中存储的信息也能留存数年甚至数十年,无需持续供电维持。因此,NAND的技术演进核心,始终围绕着如何在有限的硅片面积内,承载更多的比特数据,实现存储密度的持续提升。

从整个计算体系的定位来看,DRAM更贴近CPU、GPU等计算核心,必须与计算核心的运行速度精准适配,是存储层级中更核心的存在,其读写速度约为NAND的3000倍,二者在功能上形成互补,却无法相互替代,而功能的差异直接导向了工艺路线的彻底分野。

二者在纳米级制造层面的工艺逻辑,堪称两个完全独立的领域——若用形象的比喻,DRAM的制造是“精挖深井”的极致微缩,NAND则是“搭建高楼”的垂直堆叠,二者的工艺难度、核心痛点与技术突破方向截然不同,其中DRAM的工艺复杂度与极限挑战远超NAND,是跨界突破的核心难关。

在NAND领域,3D堆叠技术早已成为行业主流,也是提升存储密度的核心路径。工程师们通过精准的工艺控制,将存储单元垂直堆叠至数百层,在有限的硅片空间内构建起高密度的存储阵列,如同在方寸之地搭建起一座座摩天大楼。这种工艺的核心挑战集中在结构稳定性与精准度上:一方面要保证数百层薄膜的厚度均匀、材质一致,避免因层数过多导致的结构坍塌或性能衰减;另一方面,需要在极短时间内精准打通成千上万个贯穿全层的超深接触孔,确保数据能够高效传输,每一个环节的误差都可能导致整批产品报废。随着堆叠层数不断突破(已达500层以上),对薄膜沉积、刻蚀等工艺的精度要求更是达到了纳米级的极致。

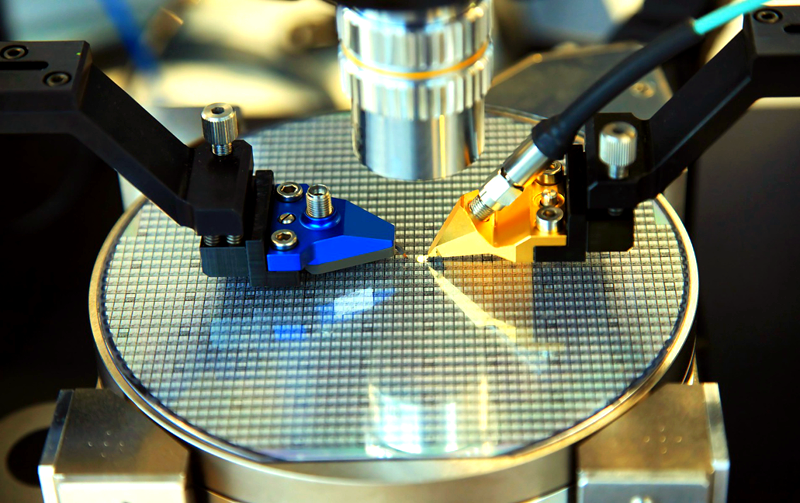

相较于NAND的“向上堆叠”,DRAM的制造更像是“向下深挖”,考验的是微缩工艺的极限突破,其难度远超NAND。每一颗DRAM存储单元都由一个晶体管和一个电容器组成,而电容器的性能直接决定了数据存储的稳定性——需要存储足够的电荷以清晰区分0和1信号,同时还要尽可能缩小体积,适配制程微缩的趋势。随着DRAM制程向14nm及以下节点推进,电容必须做得极窄且极深,形成极高的深宽比(深度与宽度的比值),这种极端结构相当于在头发丝粗细的截面上,挖掘数亿口深达数公里的深井,无论是物理层面的结构控制,还是化学层面的材料沉积,都在挑战半导体制造的极限。

业内专家指出,CPU、GPU的制造难度已被大众熟知,但DRAM的制造难度实则与高端逻辑芯片处于同一水平,二者并称制造难度最高的两类芯片。衡量芯片制造难度的核心指标之一,便是光刻机的应用——EUV(极紫外)光刻机作为全球最先进的半导体制造设备,主要用于7nm、5nm节点的CPU,以及14nm级别(1a/1b节点)的先进DRAM生产,而NAND制造则无需依赖EUV光刻机,仅通过DUV(深紫外)光刻机即可满足需求。这一差异直接印证了:先进DRAM面临的制造挑战与物理极限,与5nm、7nm高端CPU持平,均属于全球工业领域的“地狱级难度”任务,而NAND的工艺门槛与之相比差距显著,这也成为NAND厂商跨界攻坚DRAM的核心阻碍。

NAND厂商跨界DRAM的产线重构困局与成本悬崖

NAND厂商跨界攻坚DRAM,需直面产线、产业历史与量产落地的多重阻碍,每一道壁垒都需付出高昂代价。外界常误以为半导体厂房可通用,实则DRAM与NAND生产线完全无法兼容,转型需彻底重构。二者技术原理与单元结构的差异,决定核心制造设备无法复用:DRAM生产需高介电常数材料沉积设备、精密原子层沉积工具及严苛的杂质与温控标准,以保障电容结构稳定;NAND产线则侧重深孔刻蚀设备适配垂直堆叠需求。而NAND厂房的设计的全维度适配堆叠工艺,转型DRAM需清空机台、投入数十亿美元购置新设备并完成长期工艺校准,资本与时间成本极高。

从产业历史来看,DRAM市场竞争残酷、门槛极高,德国奇梦达、日本尔必达等巨头均因难以承受试错成本与周期波动黯然退场。全球现存三大存储巨头均以DRAM起家,攻克核心技术后才“降级”切入NAND市场,而从NAND逆向攻坚DRAM尚无成功先例,需重构研发范式、储备专业人才并突破专利壁垒。

即便突破技术与产线难关,从工程样品到规模化量产仍需跨越“死亡之谷”。行业对LPDDR5 DRAM样品的审慎态度,正源于此——样品仅代表实验室技术可行,DRAM良率控制极度敏感,晶圆上少量单元故障即可能导致芯片报废;且需经过1-2年下游客户认证,与高端处理器及终端厂商深度适配,信任资产积累耗时久。此外,HBM依赖先进DRAM原片集成,缺乏量产积淀则无从谈起,进一步抬高了跨界门槛。

外界往往存在认知误区,认为半导体厂房具有通用性,只需更换生产物料就能切换产品类型,实则DRAM与NAND的生产线在设备配置、工艺参数上完全无法兼容,转型意味着彻底的“重装上阵”。二者技术原理与单元结构的差异,决定了核心制造设备无法复用:DRAM生产需大量高介电常数(High-K)材料沉积设备与精密原子层沉积(ALD)工具,用于构建复杂电容结构,同时对金属杂质、温度控制的要求极致严苛,以避免电容间电荷干扰;NAND产线则侧重配置深孔刻蚀设备,适配垂直堆叠的工艺需求。

综观全局,NAND厂商向DRAM及HBM领域的跨越,本质上是一场对半导体制造极限的重新挑战。这不仅需要突破从"堆叠"到"微缩"的工艺范式转换,更要直面与高端逻辑芯片同等量级的物理极限与工程复杂度。当市场聚焦于HBM作为算力时代的关键资源时,我们更需清醒认识到:从实验室样品到稳定量产,其间横亘着材料科学、精密制造、良率控制和生态协同的四重壁垒。

中国存储产业的进阶之路,需要的不仅是投资和决心,更是对产业规律的深度理解和长期坚守。每一次工艺参数的优化、每一轮量产爬坡的积累、每一个客户认证的突破,都是在为最终的体系化突破奠定基础。这条道路注定艰辛,但也唯有穿越这些必经的挑战,才能真正在存储技术的核心领域建立起持久的竞争力。