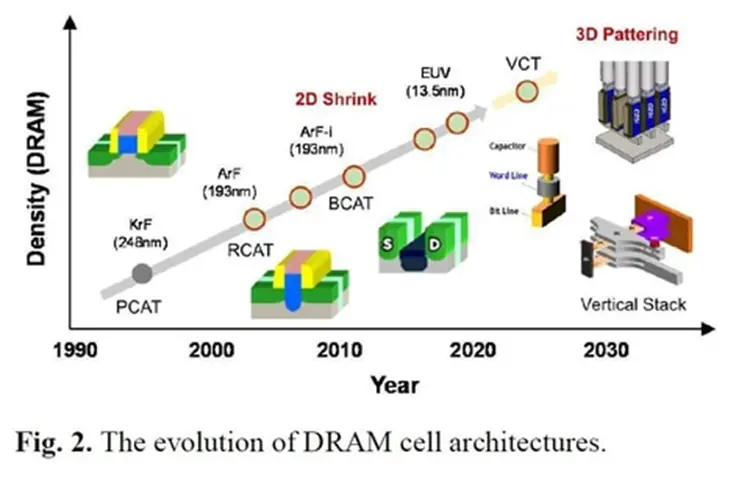

在DRAM部分,三星首先回顾了DRAM单元多年来的演变。

在 1990 年代,平面 n 沟道 MOS FET 是单元选择晶体管(单元晶体管)的标准。然而,进入21世纪,短沟道效应和关断漏电流已变得无法忽视。一种在不缩短沟道长度的情况下使横向(水平)方向微型化的晶体管结构被设计出来并被用于DRAM单元晶体管。随着光刻技术的不断缩小,DRAM单元的面积可以不断缩小。

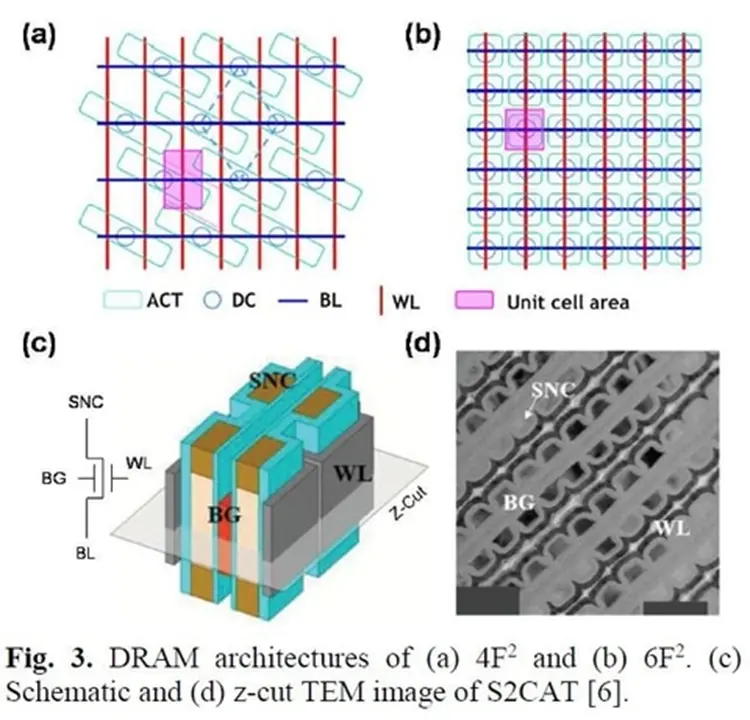

与此同时,DRAM 单元阵列布局在 2010 年代得到了改进。 DRAM单元的尺寸是根据设计规则(或最小加工尺寸)“F:特征尺寸”进行比较的。原则上,可能的最小单元是 2F(垂直尺寸)x 2F(水平尺寸)= 4F2,但这极难实现。

2010年代,通过改进DRAM单元阵列的布局,单元面积从传统的“8F2”缩小到“6F2”。即使加工尺寸相同,单元面积也减少了25%。这种“6F2”布局至今仍是大容量DRAM使用的标准。

图注:DRAM 单元的演变

(1990 年代至 2030 年代)

在“6F2”布局中,通过将字线和沟道嵌入到衬底中,单元晶体管的面积得以减小。源极和漏极水平(横向)布局。单元晶体管的垂直结构从衬底侧开始依次为字线(WL)、沟道、位线触点(BLC)、电荷存储节点触点(SNC)、位线和单元电容器。字线间距为2F,位线间距为3F。

10nm代(1X代及以后)的DRAM单元基本维持上述结构,但通过改进电容结构、字线材料等延续了七代,依次称为“1X→1Y→1Z→1A→1B→1C→1D”代。不过,下一代“0A”代(10nm以下第一代)将无法维持“6F2”布局,有很大机会转向“4F2”布局。

10nm 以下 DRAM ,如何实现

实现“4F2”布局的单元晶体管的基本结构是沟道垂直排列的结构。它被称为“VCT(垂直沟道晶体管)”。位线、沟道(侧面有字线)和电容器从基板侧垂直排列。

图注:DRAM 单元阵列布局架构和垂直通道晶体管的示例。左上为“6F2”布局,右上为“4F2”布局。左下角是三星发明的VCT(垂直通道晶体管)结构的示例(称为“S2CAT:自对准2间距单元阵列晶体管”),右下角是用透射电子显微镜(TEM)观察到的原型单元阵列的横截面图像。

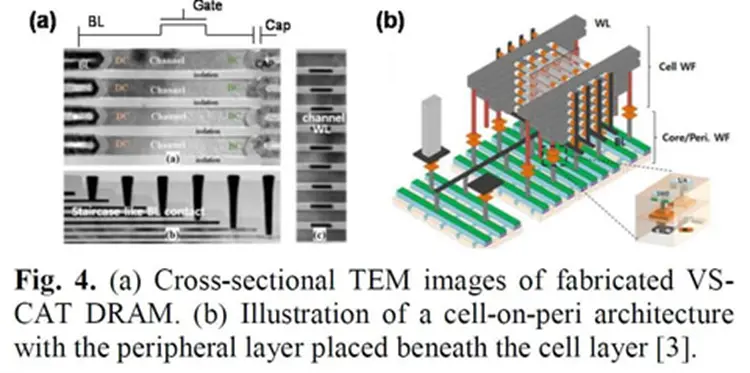

实现更高内存密度的尝试是三维 DRAM(3D DRAM)。通过垂直堆叠水平较长的 DRAM 单元(一端有位线,中间有通道,另一端有电容器)来增加内存容量。

图注:三维动态随机存取存储器(3D DRAM)的原型。这是由三星构思并制作的原型。它们被称为“VS-CAT(垂直堆叠单元阵列晶体管)”。左图显示了用透射电子显微镜 (TEM) 观察到的原型 DRAM 单元阵列的横截面。左上角显示 3D 堆叠晶体管和电容器,左下角显示位线提取结构(阶梯式),右侧显示字线和通道的横截面(一个通道夹在两条字线之间)。右侧的结构图展示了通过堆叠存储单元阵列和外围电路来减少硅面积的想法。将存储单元阵列晶圆(Cell WF)与周边电路晶圆(Core/Peri. WF)键合在一起。

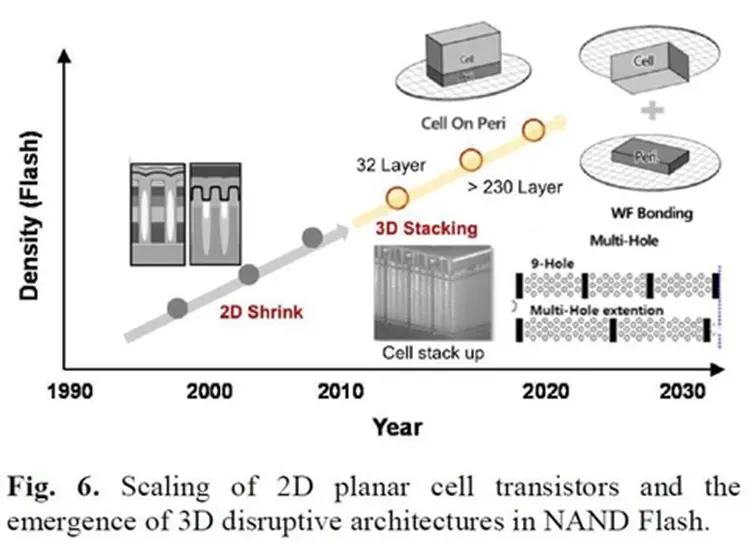

3D NAND闪存超越极限

从这里开始,将收官对有关NAND闪存(以下简称“NAND闪存”)的介绍部分进行简单说明。自上世纪90年代中期开始实用化的NAND闪存(平面NAND闪存)已经经历了密度和小型化的极限。

最初,内存容量和密度主要通过小型化来增加,但到 2010 年代初,小型化已经达到了极限。这是因为,即使存在被认为具有最高绝缘性能的气隙,也无法再抑制相邻单元(单元晶体管)之间的干扰,并且单元可以存储的电荷量已减少到无法再防止干扰的程度。

图注:NAND闪存的演变

(1990年代至2030年代)

当时的突破(突破限制的手段)就是 3D 化。作为NAND闪存基本电路的单元串(一系列单元晶体管)已从水平方向转换为垂直方向。结果,单元可存储的电荷量大大增加,相邻单元之间的干扰大大减少。

此外,该公司还利用三维NAND闪存(3D NAND闪存),成功实现了传统半导体存储器难以实现的“多值存储”成为标准规格,即在一个单元中存储三位数据。

垂直单元串通过增加堆叠单元晶体管的数量,快速增加了密度和容量。 2010 年代初期的产品有 32 层。到 2020 年代中期,它已发展到 300 多层,高度约为其原始高度的十倍。此外,将存储单元阵列堆叠在外围电路上方(CuA:CMOS under Array)的布局已投入实际使用,从而减少了硅片面积。

与此同时,3D NAND闪存面临着与其前身平面NAND闪存类似的挑战。随着堆叠的增加,形成单元串沟道的孔变得更深,使得蚀刻更加困难。为了缓解这个问题,单元晶体管的栅极(字线)和字线之间的绝缘膜已经逐渐变薄。这会增加同一单元串中相邻单元之间的干扰,并减少可积累的电荷量。

此外,构成单元串通道的孔(存储孔)之间的间距也逐渐缩小,有助于提高存储密度。这增加了相邻单元串之间的干扰。

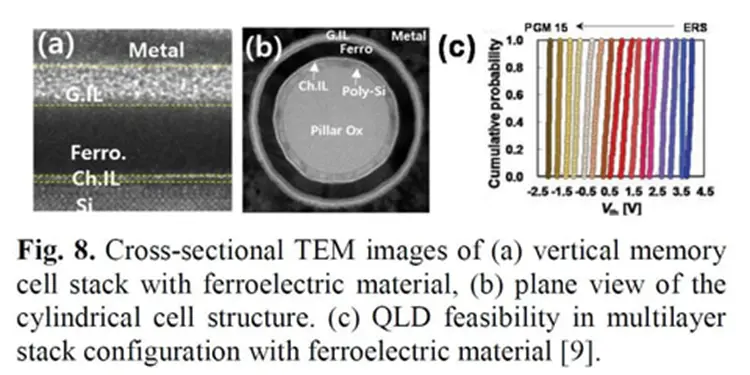

为了解决这个问题,人们尝试用电荷陷阱单元中的铁电膜代替作为栅极绝缘膜的氮氧化物 (ONO) 膜。电荷陷阱法是通过在ONO膜的捕获能级中积累电荷(主要是传导电子)来决定逻辑值(1bit的“高”或“低”)。铁电薄膜的逻辑值由极化方向决定,而不是由电荷决定。

通过在单元晶体管中使用铁电膜,可以实现降低编程电压和抑制阈值电压波动等效果。这两者都有助于减少小区之间的干扰。在单元级别上也已确认可以支持“多值存储”,即将单元晶体管的阈值电压从两个值增加到八个值(3 位)或 16 个值(4 位)。

图注:将铁电薄膜应用于 NAND 闪存单元晶体管的尝试示例。最左边的图像(a)是包含铁电膜(Ferro)的绝缘膜的横截面图像(通过 TEM)。中心(b)是将铁电薄膜纳入类似于 NAND 闪存的圆柱形结构的单元晶体管的横截面图像(TEM)。最右边(c)显示了阈值电压以16种不同的方式变化时的测量结果(相当于4位/单元)

DRAM 和 NAND 闪存都面临着许多阻碍其未来发展的挑战。三星在主题演讲中提到的只是其中的一部分。我希望能够找到解决这些问题和其他问题的解决方案,并且希望进步能够继续下去。

更多技术分享

在演讲中,来自全球的企业和专家对DRAM和NAND的未来做了丰富的分享。

例如imec首次公布纯金属栅极技术,该技术可将层间距缩小至30nm,同时确保3D NAND闪存的可靠性。铠侠也分享了其多级编码技术,该技术可实现闪存的高速随机存取。应用材料公司开发出一种快速外延生长3D NAND的Si沟道的技术。

除了3D NAND,GLOBALFOUNDRIES还将展示兼容28nm HKMG CMOS逻辑的分栅嵌入式闪存技术。他们演示了一个34Mbit嵌入式闪存宏的原型。

在“DRAM”领域,开发3D存储器技术的风险投资公司NEO Semiconductor将讲解与3D NAND结构类似的3D DRAM技术“3D X-DRAM”。内存供应商 Macronix International 将展示一种改进的 3D DRAM 技术,该技术由两条水平字线、一条垂直位线和栅极控制晶闸管组成。半导体能源实验室 (SEL) 通过使用氧化物半导体单片堆叠平面 FET 和垂直通道 FET,制造出了原型 1M 位 3D DRAM。

在“铁电存储器”领域,美光科技讲解了其高性能、长寿命铁电存储器的材料工程技术。佐治亚理工学院将描述一种非挥发性电容器的制造工艺,该工艺能够实现铁电电容器的小信号无损读出。GLOBALFOUNDRIES 也讨论了互补 FeFET 存储器中发生的电荷捕获问题,该存储器旨在嵌入 CMOS 逻辑。

在“电阻式存储器/交叉点”领域,清华大学将展示兼容40nm高压CMOS工艺的3.75Mbit嵌入式电阻式存储器宏。此外,旺宏国际开发了AsSeGeS和GeN异质结构,优化了交叉点存储器中使用的OTS选择器的性能。

【来源:半导体行业观察】