6月11日消息,据媒体报道,台积电将于2026年在其子公司采钰设立首条CoPoS封装技术实验线。与此同时,用于大规模生产的CoPoS量产工厂也已确定选址嘉义AP七,目标是在2028年底至2029年间实现该技术的大规模量产。

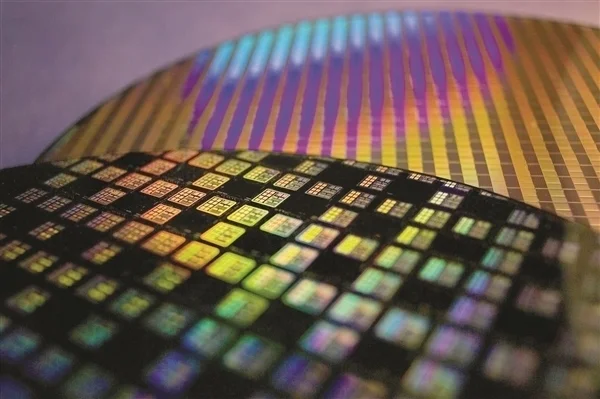

CoPoS是台积电推出的一项创新封装概念,其核心在于“化圆为方”——摒弃传统的圆形晶圆,直接将芯片排列在大型方形面板基板上进行封装。这种设计可视为对现有CoWoS-L或CoWoS-R技术的矩形化演进。关键优势在于:方形基板提供更大的可利用空间,从而显著提升单位面积产出效益并有效降低成本。此外,CoPoS封装结构更具灵活性,能更好地适应多样化的芯片尺寸与应用需求。

据悉,CoPoS技术将主要聚焦于人工智能(AI)等高端芯片应用。其中,采用CoWoS-R制程的版本将主要服务于博通,而CoWoS-L则主要面向英伟达(NVIDIA)及AMD。

行业分析指出,这种“化圆为方”的方式不仅大幅提升了产能和基板面积利用率,更使其在人工智能(AI)、5G通信及高性能计算(HPC)等对先进封装有极高需求的领域展现出强大的竞争力。

值得注意的是,台积电此次选择在采钰设立CoPoS实验线,延续了其一贯的战略布局思路。此前在布局面板级封装(PLP)时,采钰及其关联公司精材就因在光学领域的深厚积累而被考虑作为实验线选址。这一选择也为其未来进一步整合硅光子(SiPh)、共封装光学(CPO)等前沿技术趋势奠定了基础。

【来源:快科技】