于NAND方面,甚至在包括NAND和DRAM在内的存储方面,SK海力士过去多年无论是在技术还是市场份额一直以来都是落后于韩国竞争对手三星。

但据韩媒Businesskorea在10月底的报道透露,得益于在HBM上的成功,SK 海力士半导体业务部门的年度营业利润将首次领先于 。这一发展标志着全球半导体行业竞争格局的重大转变,三星在该行业传统上占据主导地位。(具体细节可以参考我们之前的文章《韩国芯片,变天了》)

但现在,三星的另一个固有阵地NAND,也正在面临SK海力士的冲击。作为NAND 市场的领导者,据相关报告披露,截止2024年二季度,三星占有NAND市场 36.9% 的份额。但作为追逐者的SK海力士(涵括SK Hynix 和 Solidigm ),其在全球NAND市场的份额从2020年的11.7%增长到2024年第二季度的22.5%。报告进一步指出,如果这一趋势持续下去,单纯SK海力士的年市场份额预计将在 2024 年首次超过 20%。

在新的NAND发布之后,SK海力士打出了追逐三星的重要一枪。

321层TLC NAND闪存,首超三星

据韩媒上月的报道,SK Hynix 刚刚超越了竞争对手三星。这家全球第二大内存芯片制造商已成为业内第一家量产 321 层三层单元 NAND 的公司。这一进步将以实惠的价格实现更高容量的内存。

SK Hynix 最近发布了其新的 1 兆位 4D NAND 芯片,创下了新纪录。该公司势头强劲,不到一年前它还率先推出了 238 层 NAND。与之前的发布一样,321 层的突破意义重大,因为它可以显著提高消费者和企业 SSD 的存储密度。

密集排列的芯片可能使容量超过 100TB 的 SSD 价格更便宜。这种 NAND 将特别适用于人工智能数据中心,尽管其他需要高能效存储且性能要求高的应用也应该会从中受益。

SK Hynix 利用巧妙的工艺优化,将 300 多个层塞入单个 NAND 中。该公司的新“Three Plugs”技术通过优化的电气连接工艺同时连接三个存储层垂直通道。该工艺以出色的制造效率而闻名,并利用具有自动对准校正功能的低应力材料。

然而,连接所有这些层会产生应力和对准问题,SK Hynix 必须克服这些问题。该公司通过开发新的低应力材料和自动对准校正来克服这一问题,以便在制造过程中保持一切井然有序。

新工艺还通过重复使用与 238 层 NAND 相同的平台,将生产效率与上一代产品相比提高了59%。这些效率改进意味着市场上性能更佳、成本更低。该公司声称,与 238 层 NAND 相比,新的 321 层芯片的数据传输速度提高了 12%,读取速度提高了 13%,能效提高了 10% 以上。

SK 海力士计划逐步扩大 321-high 产品的使用范围,瞄准需要低功耗和高性能的新兴人工智能 (AI) 应用。SK 海力士 NAND 开发主管 Jungdal Choi 表示,这一进步使该公司更接近引领 AI 存储市场,其中包括用于 AI 数据中心和设备上 AI 的固态硬盘 (SSD)。他指出,SK 海力士正在通过扩大其在超高性能 NAND 领域的产品组合以及以高带宽内存 (HBM) 为主导的 DRAM 业务,向成为综合 AI 内存提供商的方向迈进。

韩媒Chosun Biz指出,虽然 SK 海力士在 NAND 市场份额方面仍落后于三星,但它在垂直堆叠单元技术方面处于领先地位,这表明 NAND 市场可能会发生重大变化。

面对这个发布,三星强势回击。

三星正在开发 400 多层 3D NAND

据消息报道,三星目前正在开发286 层的第九代 3D NAND ,并正在开发 400 层技术。这是通过 2025 年 IEEE 国际固态电路会议议程发布透露。

据介绍,这款 1 兆位 NAND 芯片的密度为 28 Gb/mm2,层数超过 400 层,采用三级单元 (3b) 格式,将成为三星 V-NAND 技术的第十代产品。第九代芯片采用双串堆叠,有 2 x 143 层,有 TLC 和QLC(4 位/单元)两种格式。第九代 V-NAND 支持高达 3.2 Gbps 的数据速度,而新的 400 层以上技术则支持每针 5.6 Gbps,速度提高了 75%。该速度似乎既适合 PCIe 5,也适合两倍快的 PCIe 6 互连。

在400层的NAND上,预计将采用三层堆栈架构,而不是当前的双层堆栈设计。这一进步充分利用了三星在层数方面的领先优势,因为它是唯一一家能够在单个堆栈中生产超过 160 层的公司,而竞争对手只能达到 120-130 层。如果三星选择三层堆栈方法,该公司可以实现惊人的 480 层。

其中,“WF-Bonding”则是三星实现这个层数的关键技术。据介绍,这是一项名为晶圆到晶圆键合的技术,其中两个单独的 NAND 晶圆(其上已制造单元和/或电路)相互连接。这种键合使每个晶圆的制造工艺在可扩展性、性能和产量方面得到优化。

三星表示,这种方法将实现具有大存储容量和出色的硬盘性能的“超高”NAND 堆栈,非常适合 AI 数据中心的超高容量固态硬盘 (SSD)。据该公司称,这款芯片被被称为键合垂直NANDFlash,或BV NAND,是“人工智能的梦幻NAND”。

2013年,三星率先推出V NAND芯片,推出垂直垂直存储单元——这是一个完整的产品。据三星称,其BV NAND单位面积密度提高1.6倍。

三星计划于 2027 年推出 V11 NAND,进一步开发其速度惊人的技术,将数据输入和输出提高 50%。该公司还计划推出SSD订阅服务,面向希望管理高昂AI半导体投资成本的科技公司。

除了400层NAND之外,三星电子明年还将增加其先进产品线的产量,双重回应。该公司计划在平泽园区安装新的第9代(286层)生产设施,月产能为30,000至40,000片晶圆。此外,在中国西安工厂,三星将继续将128层(V6)NAND生产线转换为236层(V8)产品工艺。

其他厂商的亦步亦趋

由于分层竞争激烈,预计2025年NAND时代将进入400层,2027年将达到1000层。韩国业内专家认为,三星、SK海力士、美光等都将在2025年推出400层NAND产品。至于1000层NAND ,也是包括铠侠在内所有NAND厂商的目标。

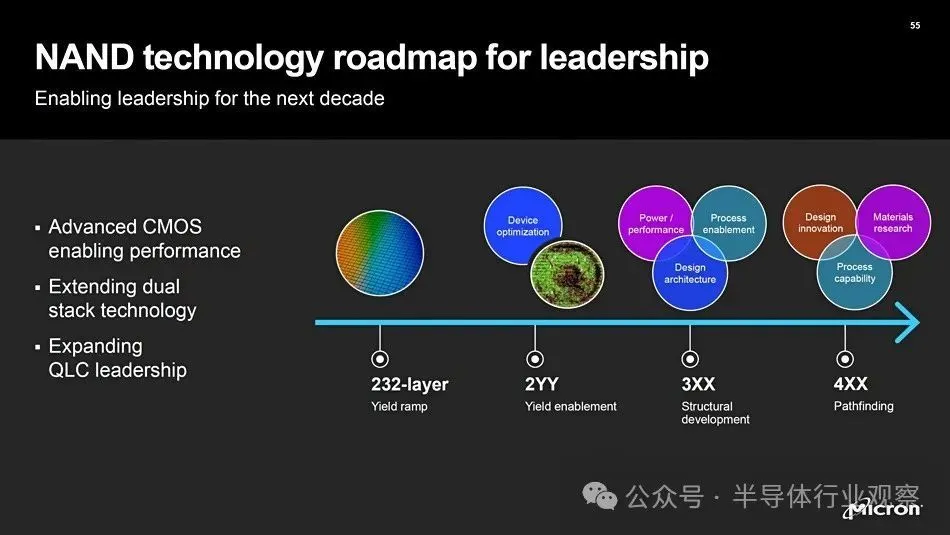

首先看美光方面,早在2022年,他们就发布了将NAND层数增加到 400 层以上的路线图。

据报道,在这个产品中,他们将使用双堆叠技术——是指将两个 3D NAND 芯片堆叠在一起,即所谓的“串堆叠”。这克服了半导体制造中的难题,例如随着层数的增加,需要在层间蚀刻连接孔。随着孔深度的加深,这些孔的侧面可能会变形,并阻止 NAND 单元正常运行。

美光表示,其重点是 QLC(4 位/单元)NAND,但并未提及使用PLC(五级单元)将单元位数增加到 5 ,西部数据正在研究此技术,Soldigm 正在开发。我们认为这是因为美光很谨慎,而不是因为 PLC NAND 不可行而拒绝了它。

西部数据则认为,层数稍高并不具有内在优势,因为它正在横向缩小单元尺寸(宽度和长度),并通过增加层数来增加芯片高度。这两种技术的结合意味着它可以将芯片密度提高到与竞争对手相同或更高的程度,并且层数更少。

往下走,1000层也成为了厂商的目标。

例如铠侠在今年于首尔举行的国际内存技术研讨会上表示,公司制定了雄心勃勃的路线图,到 2027 年实现惊人的 1,000 层 3D NAND 闪存。三星之前也曾表示,计划在 2030 年之前开发出层数超过 1,000 层的 NAND,但要实现这一目标绝非易事。

据日本媒体 PC Watch报道, Kioxia 的预测是基于过去的趋势推断,并改进了现有的 NAND 单元技术。该公司预计,NAND 芯片密度将在三年内达到 100 Gbit/mm2,存储单元层数为 1,000。要实现这一目标,增长率必须保持在每年1.33 倍。

至于三星方面,韩国科学技术院 (KAIST) 的研究人员此前曾展示其关于使用 Hafnia 铁电体作为 1,000 层以上 QLC NAND 的“关键推动因素”的研究成果,这将是非挥发性存储领域的分水岭成就,这也被认为是三星可能的技术方向。

正如 Wccftech所指出的,对 Hafnia 铁电体的研究具有开创性,而且距离实现仍需数年时间,因为尽管研究仍在进行中,但该技术尚未完全被理解。然而,如果它被证明足够可靠,可以取代现有技术,那么它就可以制造出更小的电子元件。尽管三星没有直接参与这项研究,但据报道,从事这项研究的团队与三星是一致的。据信,如果取得足够的成果,他们所做的工作将在某个时候直接转移到三星的实验室。

然而,扩展到四位数的层数并非易事。据存储新闻网站Blocks & Files称,使用 3D NAND 实现更高密度不仅仅是在芯片上添加更多层。每层都需要一个暴露的边缘来实现存储单元之间的连接,从而形成阶梯状的芯片轮廓。因此,随着层数的增加,阶梯结构占用的面积会大幅增加,从而抵消部分密度增益。

为了弥补这一点,内存制造商需要在向 QLC NAND 过渡时纵向和横向缩小 NAND 单元,与当今的 TLC 技术相比,每个单元可容纳 4 位。随着层的增加,通道电阻和信号噪声也成为成长的烦恼。

总之,NAND Flash的竞争,方兴未艾。

【来源:半导体行业观察】