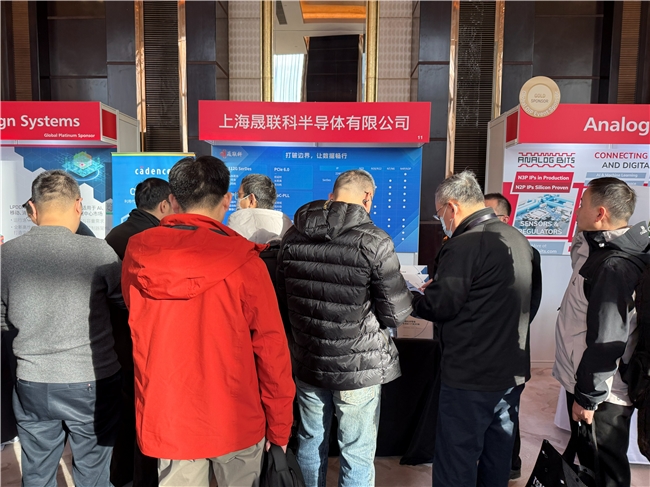

12月4日,TSMC China OIP Ecosystem Forum 在南京盛大启幕。作为 TSMC 重要的 IP 合作伙伴,晟联科携全系列高速接口 IP 解决方案惊艳亮相11号展台,其中PCIe 5.0/6.0 PHY+CTRL 一体化方案的现场演示尤为亮眼,不仅实现5.0 应用与Transaction Layer 和 Physical Layer的高速互通测试,还实现了PCIe 测试板与Server CPU 的高速互通,成为展会现场备受瞩目的焦点。

PCIe PHY+CTRL方案打通 Server CPU 高速互联链路

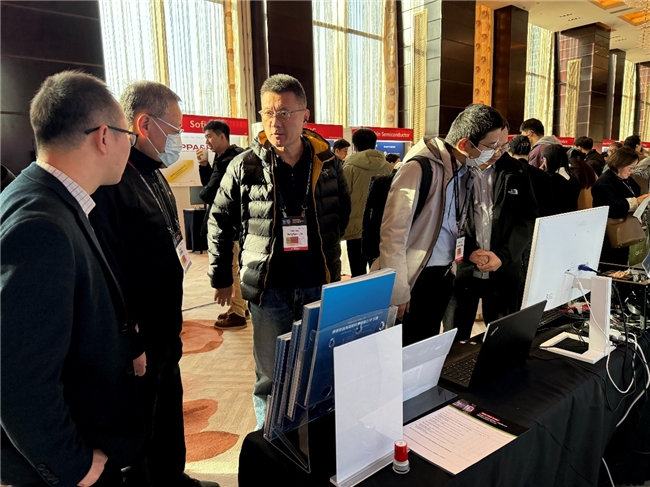

在TSMC China OIP的核心展区,一块连接着 Server CPU 的测试板前始终人头攒动 —— 这里正在上演晟联科PCIe PHY+CTRL 方案的实时互通演示。

显示器上清晰呈现出稳定的数据以超高带宽在AXI SRAM和主机 memory之间测通过PCIe接口顺畅收发,8秒可以完成100000次16k的DMA数据传输。无卡顿、低延时的高速互通吸引了现场专业观众纷纷驻足观看、拍照记录,不少行业伙伴更是上前与晟联科技术专家沟通,咨询技术细节。

“今天看到晟联科的PCIe IP芯片能直接与商用 Server CPU全栈集成成功,还能做到稳定的高速传输,确实超出预期。” 现场一位来自数据中心芯片设计企业的工程师,在近距离观察演示后坦言。

这种 “即集成、即能用” 的特性,正是晟联科 PCIe PHY+CTRL 方案的核心优势:通过 PHY 与 CTRL 的深度协同优化,无需额外开发适配接口,大幅降低客户集成成本,缩短产品上市周期,完美契合数据中心、高性能计算(HPC)等场景对 “快速部署、稳定运行” 的刚需。

作为面向下一代高速互联需求的旗舰产品,晟联科PCIe 6.0 IP在性能、功耗、兼容性等多维度实现突破,具体亮点如下:

PCIe 6.0 IP关键性能

· PAM4 和 NRZ 信号技术,专为 PCIe 应用设计;

· 每通道支持2.5, 5, 8, 16, 32 and 64 GT/s PCIe数据,支持X16, X8, X4 通道宽度;

· 符合 PIPE 6.2.1 规范;

· 采用512b AXI总线架构和32b(Gen5)/64b(Gen6) PIPE 接口,实现高速 /低延时;

· 基于 DAC 的 PAM4 发射器,包含(FFE)前向均衡;

· 通过读写寄存器提供广泛的 PMA 调试功能;

· 灵活的用户界面以及 AXI4/ 原生接口;

· 主要功能支持软件控制;

· 支持通道分叉(可配置);

· 每个 SerDes 通道均可独立开启 / 关闭电源;

· 在核心生成阶段,可按需开启或关闭特定功能,以优化门控计数控制器。

深耕高速接口领域,共筑产业新未来

作为 TSMC OIP 生态的重要参与者,晟联科此次亮相不仅是对自身 PCIe 技术实力的一次全面展示,更是与产业链伙伴深化合作、共促发展的重要契机。依托 TSMC 先进的工艺平台,晟联科的112G SerDes、PCIe6.0、32G UCIe 系列IP已完成多节点验证,具备成熟的量产交付能力,可快速响应客户的商业化需求。

未来,晟联科将持续聚焦 PCIe 技术的迭代与创新,紧跟 PCIe 7.0 等下一代协议的发展趋势,不断优化方案性能与体验。同时,晟联科也将继续深度融入 TSMC OIP 生态,与全球合作伙伴携手,为数据中心、高性能计算、AI 等领域提供更高效、更可靠的高速接口解决方案,共同推动半导体产业高速互联技术迈上新台阶。

互动福利:解锁 PCIe 技术新机遇

如果您对 PCIe 6.0/5.0/4.0 IP方案感兴趣,欢迎扫描下方二维码填写信息获取详细资料。同时,留下您的联系方式,还有机会获得晟联科定制的精美礼品,与我们的技术专家一对一交流,解锁高速互联的无限可能!